记录一次Excel在Timing Closure中的应用

本文旨在记录一次STA timing closure过程中如何利用Excel表格工具可视化的优化inter-clock skew,从而大大降低DMSA timing ECO的代价。

【Background】

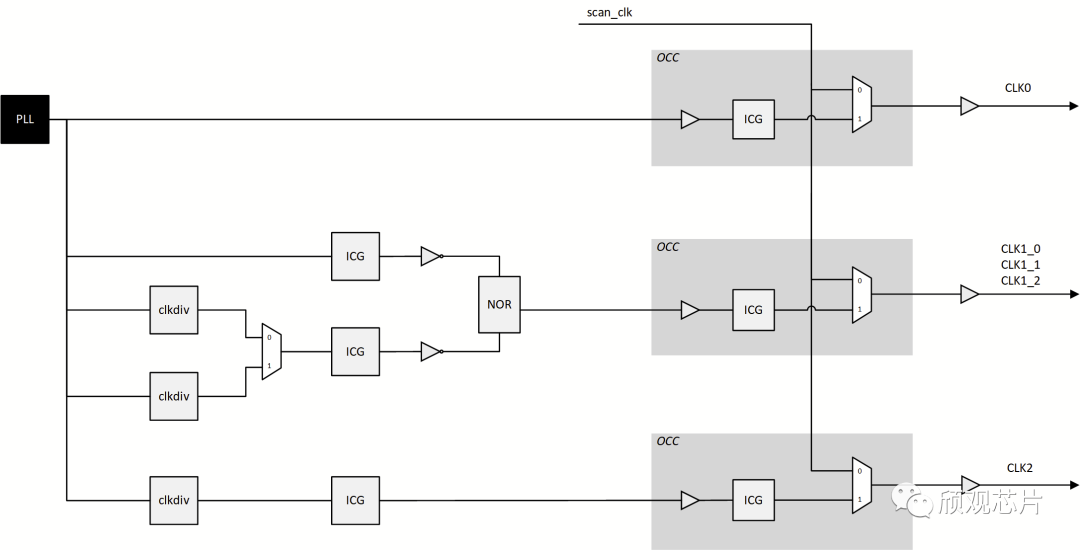

这次timing closure的难点在于design有5个同步异频的clock。所谓同步异频是指这5个clock的source clock相同,但是经过了不同的clock divider, clock gating, 以及clock mux。clock structure简化为如下图所示:

- Generated clock从PLL出来就分叉:OCV严重

- PLL clock频率巨高:>1000MHz

- 三个clock group两两之间都有talk:CLK0, CLK1_0/CLK1_1/CLK1_2, CLK2。

CTS clock skew已经控制得很好了,CTS report global skew小于100ps。但是post-route timing显示hold time TNS数量巨多,WNS数值巨大,尤其是inter-clock之间问题尤为严峻,而且各个方向上都有。

【Analysis】

通过分析timing violation的数值和方向,决定在做DMSA fix timing ECO 之前,对clock latency先做微调,以期达到尽量减小TNS和WNS,从而降低timing ECO的开销。虽然不同PVT corner下的violation情况不尽相同,但是大体趋势是基本相同的,所以调整clock latency只需要盯着一个corner即可,本例考察的是slow-40c下。

此时敏锐同学不禁要问:既然clock skew已经控制的很好,那调整clock latency岂不是很有可能会把skew调的更差,尤其是local skew?没错,clock skew极有可能会变差。可是,但是,timing closure的目的是close setup & hold,控制clock skew不是目的,而是手段,只要有利于降低TNS/WNS,即使skew变大,也是正确的方向。

【Solution】

那么下面来看看,我是如何利用Excel快速找到调整clock latency的方向和数值的。

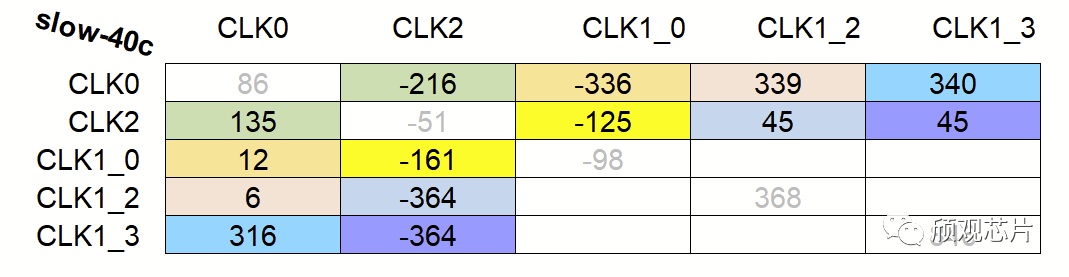

第一步:把clock以及inter-clock的WNS在Excel中以matrix的形式列出来,如下图所示:

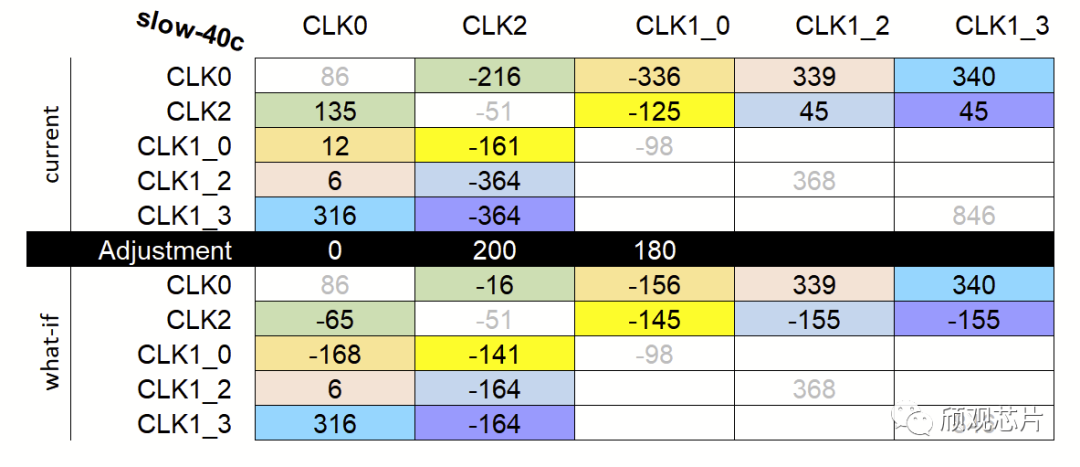

第二步:做”what-if adjustment”,在上表的基础上增加Adjustment行,以及通过调整某个或某几个clock latency后的what-if结果。what-if timing结果是利用Excel公式计算所得,如下图所示:

第三步:反复调整Adjustment的值,直到获得满意的what-if timing结果。通常尽量调到WNS>0,如果无法达到WNS>0,那就使得inter-clock相互之间的WNS尽量balance。

第四步:在STA中apply上述clock adjustment value,研究调整后timing结果,考察WNS是否和上表中的what-if结果接近,同时也考察TNS是否满意,如果对STA结果不满意,可以回到第三步对clock latency再次进行调整。

第五步:在PnR中apply上述clock adjustment value,此时要考验PnR对调整clock delay的经验了。如果结果符合预期就可以进行DMSA了,后面的timing closure flow和本文无关,此处不做赘述。

【Summary】

- 在OCV很大的inter-clock电路中,调整clock skew后考察WNS/TNS比单纯的追求最小化skew对timing closure更有帮助;

- 利用Excel表格调整clock latency并做what-if计算timing的好处是:快速、可视化;

- 本文提到latency调整是作用于generated clock source上,所以仅适用于inter-clock timing,而intra-clock timing不受影响;

- 本文的方法对修setup或hold都适用。