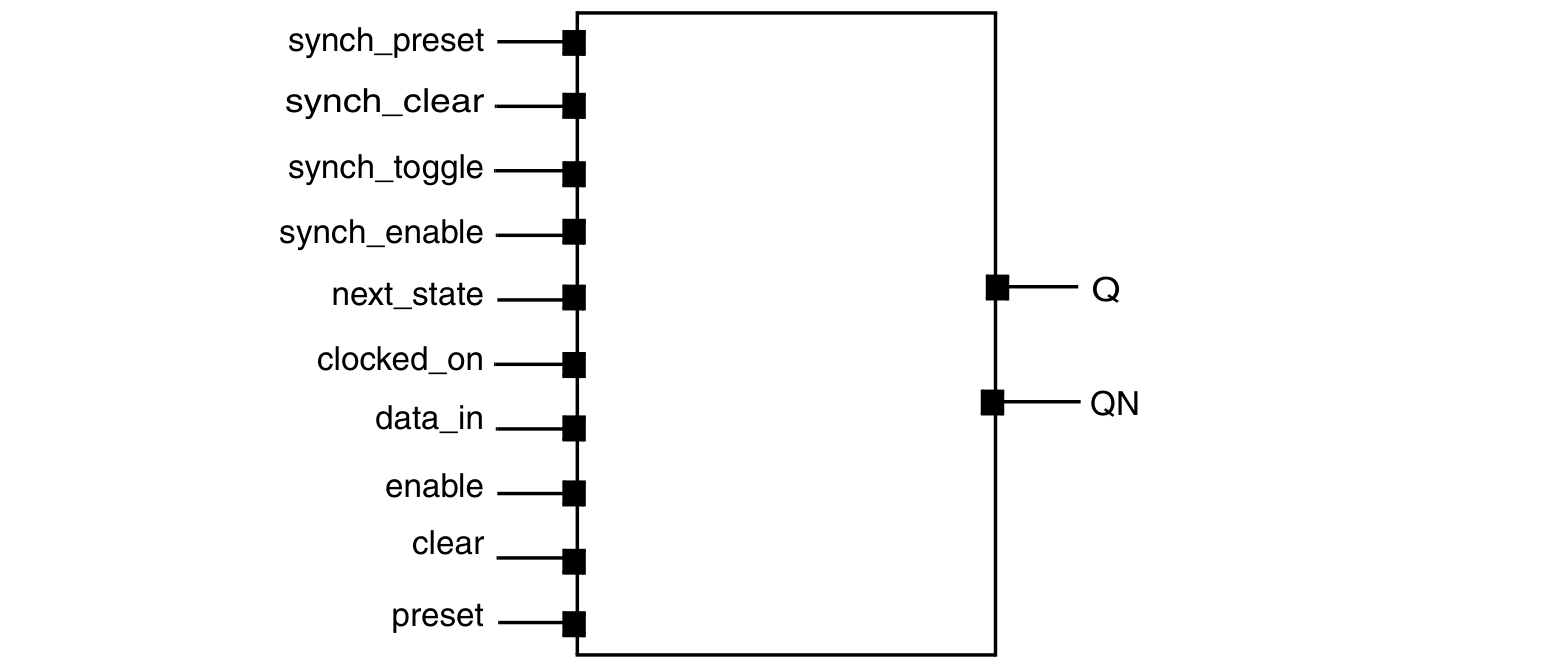

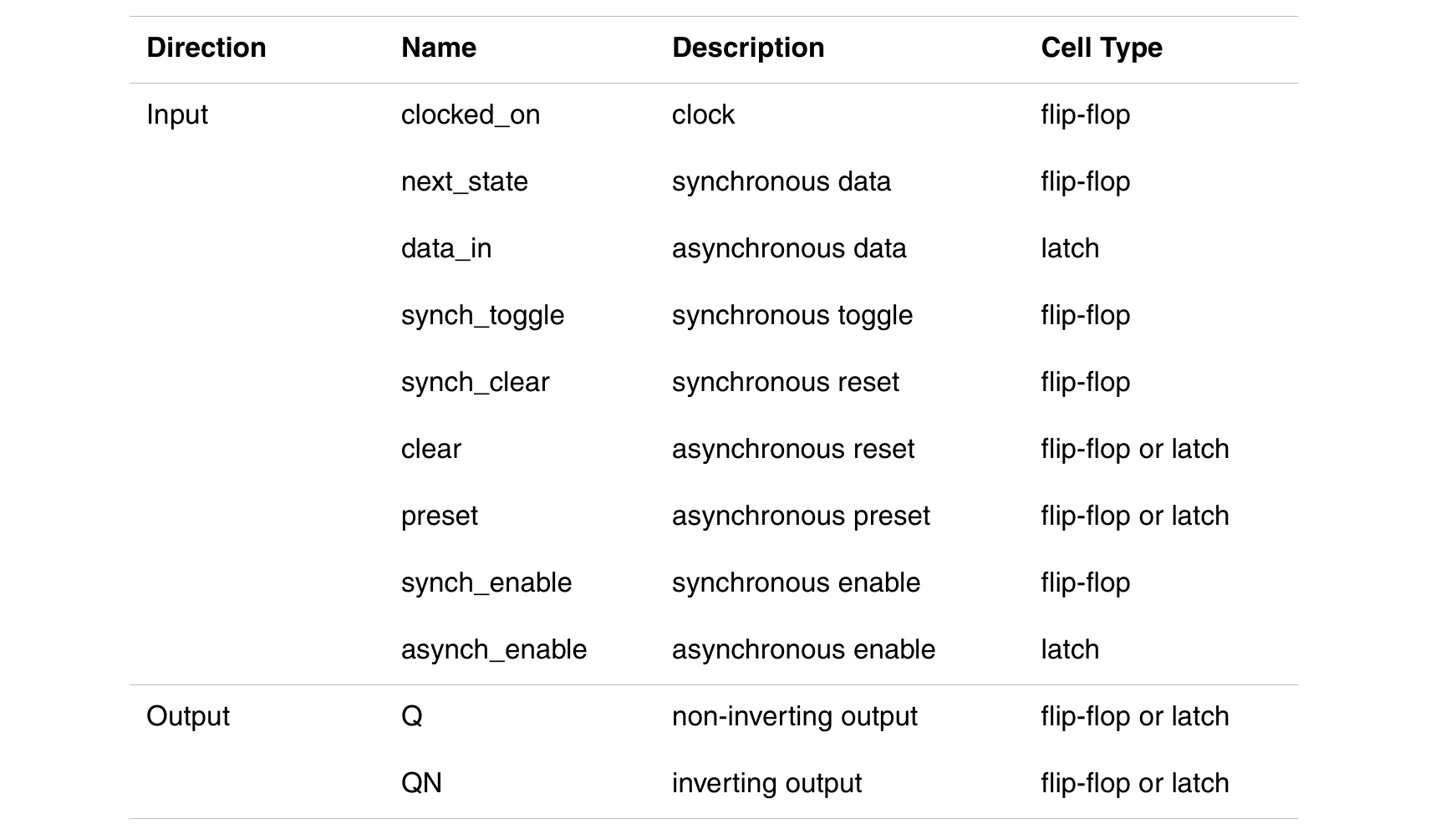

GTECH Flip-Flop Cell

When HDL Compiler reads in a Verilog or VHDL RTL description of the design, it translates

the design into a technology-independent representation (GTECH). In GTECH, both

registers and latches are represented by a SEQGEN cell, which is a

technology-independent model of a sequential element as shown in the figure below. SEQGEN

cells have all the possible control and data pins that can be present on a sequential element.

Knowing this is important and useful when you would set constraint on a register in the synthesis phase of HDL mapping, e.g.,

1 | set_multicycle_path -from [get_pins A_Example_reg/clocked_on] |

Refer to the document of ‘Design Compiler Optimization Reference Manual’ for details.