判决反馈均衡器(上)

判决反馈均衡器(下)»

Part1 DFE基本概念

判决反馈均衡器(Decision Feedback Equalizer, DFE),是目前SerDes中常见于于RX部分的一种均衡方式,能够有效提升RX的接收性能。

先前我们在讲均衡之FFE中提到了信道的时域响应存在拖尾现象,拖尾会影响到下一个码元,也就是常说的码间干扰(ISI),当然信道的非理想还包含串扰,反射等现象。对于比较高的信道插损,线性均衡CTLE的效果存在上限,需要进一步的均衡机制。

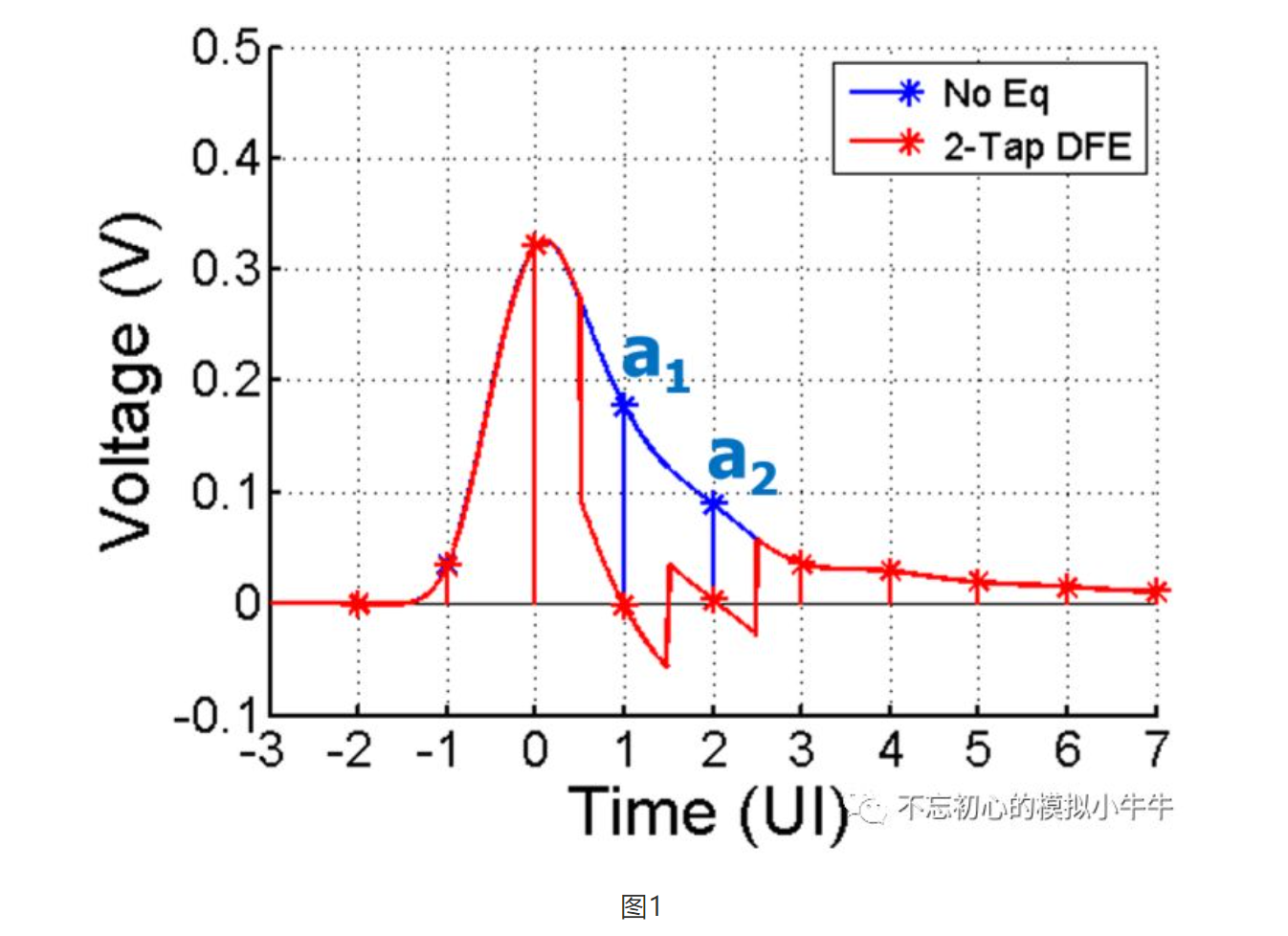

如图1,时域上,一种最直接原始的想法是,如果能够根据当前码元的判决结果,将该码元的后续影响依次全部消减,就可以把当前码元ISI的影响降到最低,甚至消除。这也是DFE作用最直观的描述。

基于上述思路,那么重点就是该如何实施和实现,如何做到对信道的自适应,系统的鲁棒性如何提高,算法如何设计的高效等一些列问题?本系列将试着研究回答这些问题。

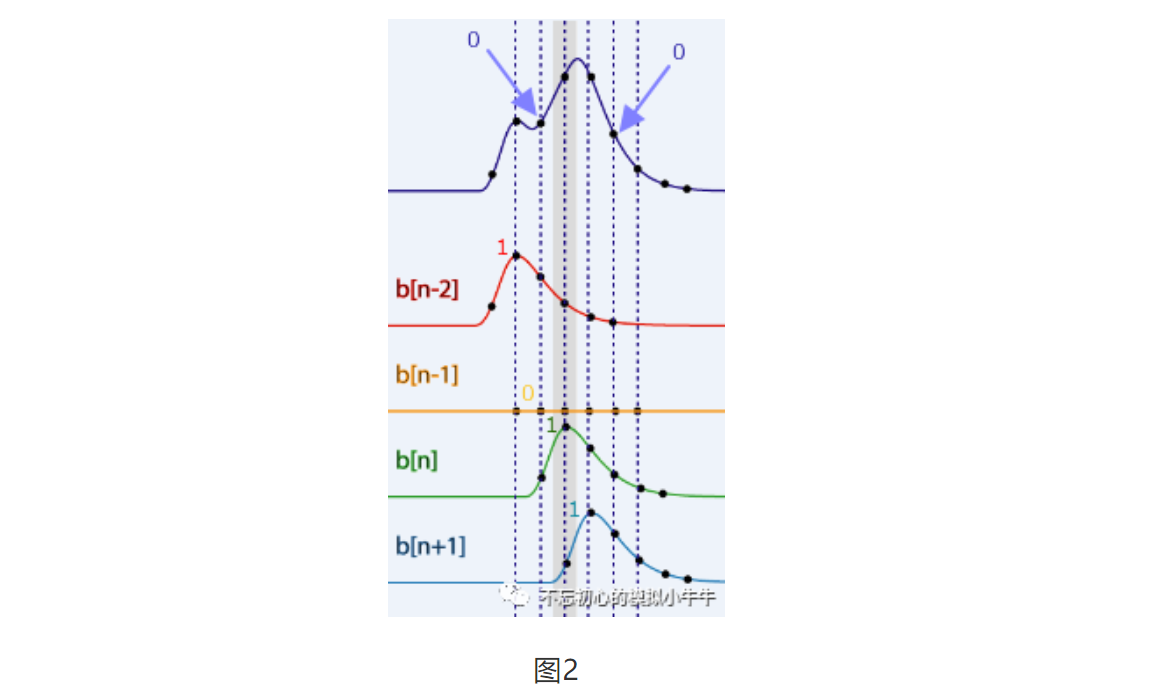

图2单脉冲冲激响应包含了3个后标(postcursor)量,1011的数据经过信道后的波形是对应脉冲移位叠加的结果。其中第二个数据0很容易出现误判。如果能够准确的判断第一个码元的话,将结果延迟反馈到输入信号处,并适当减掉部分量,则第二个码元0就更容易判断准确。这也是判决反馈均衡器(Decision Feedback Equalizer)的字面含义。

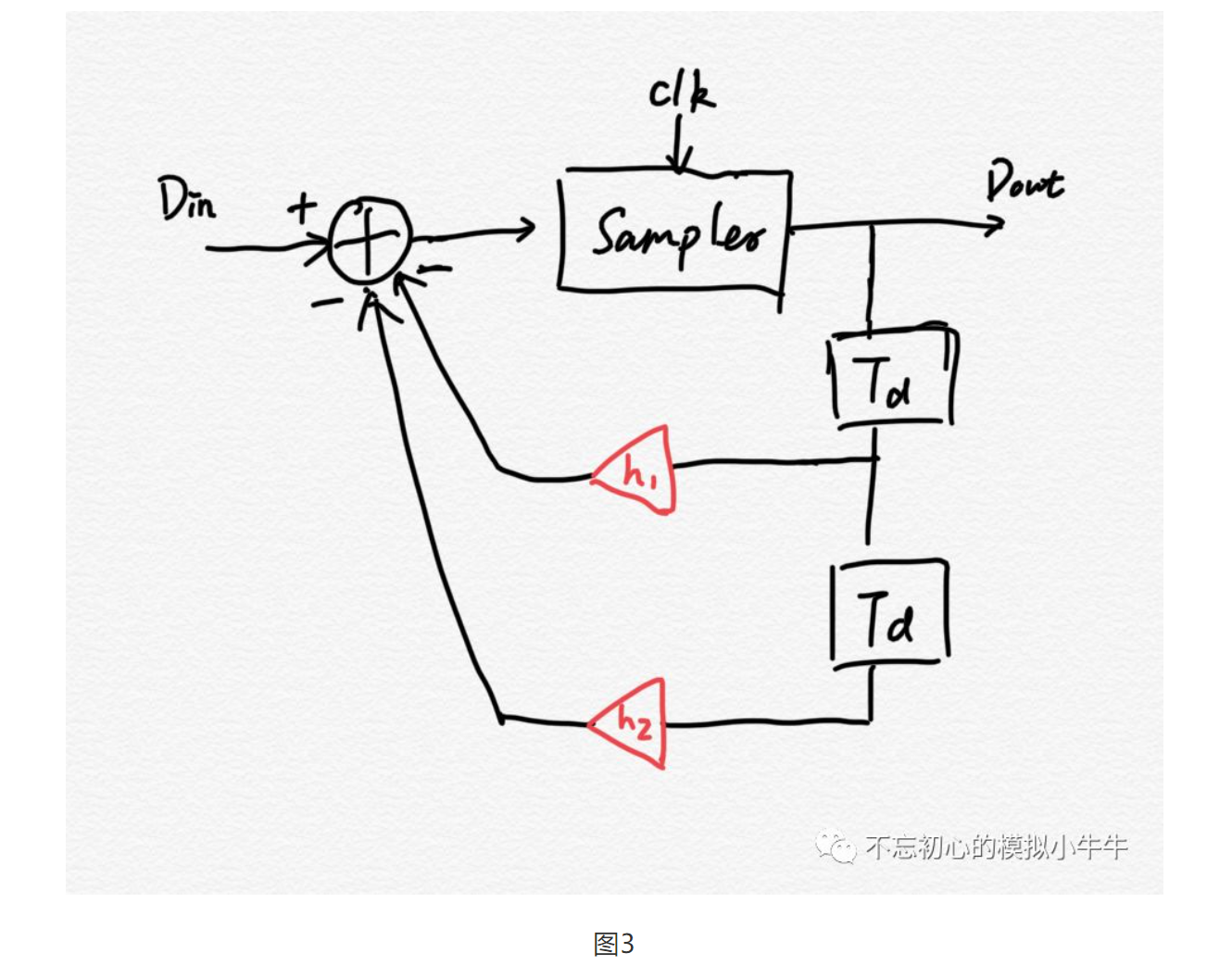

实现时,对于连续输入数据Din,通过时钟Clk控制的采样器Sampler,得到采样数据Dout,经过Td的延迟,通过权重h1和h2与输入数据相加。合适的延迟时间td和权重h1,h2就能保证将输入数据的码间干扰降低或完全消除,如图3。

图3结构,需要考虑如下两个问题:

第一,Dout如果仅仅是采样输入数据Din,会存在量化精度的问题,比如用多少位表示。量化后的信号,需要决定反馈的权重h1和h2的大小及符号,对于NRZ编码的信号,采样后可用1bit的量化器量化为逻辑信号0和1。对于PAM4编码的信号,采用后通常会采用多bit的量化器(比如用ADC实现)。方便后续的数据处理。

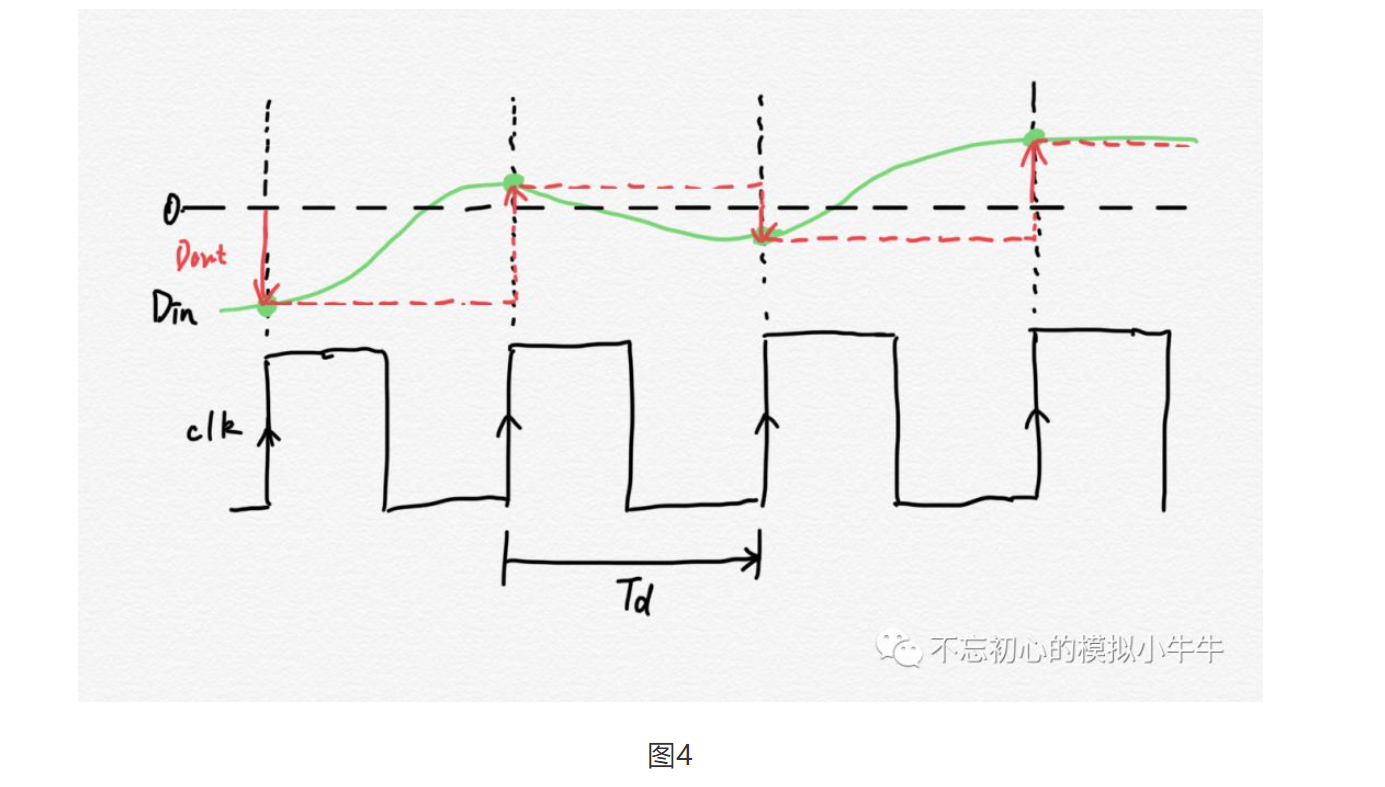

第二,延迟时间Td。如图4所示,全速率的RX结构,假如用上升沿采样数据,需要在一个采样时钟周期,也就是需要1个UI的时间内,将前一个UI的影响体现到后续的采样数据上。这里可以简单的理解Td<1UI。如果不满足,则无法体现消除效果。

注意NRZ编码的采样器量化后,转化为1bit逻辑,是非线性的转化过程。

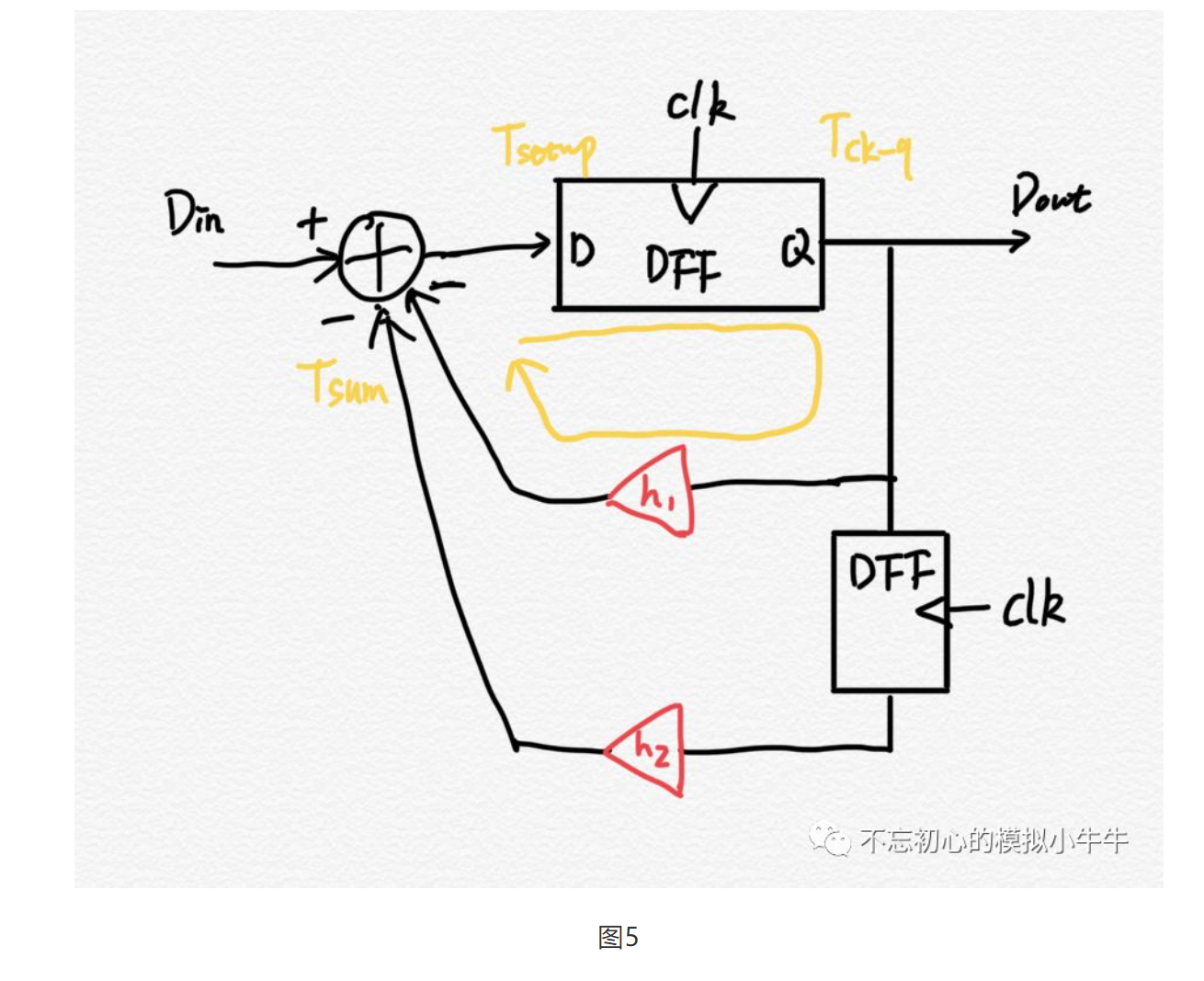

实际电路实现时,采样器也叫Slicer,Slicer和延迟单元合并起来可以用DFF来表示。如图4所示,其中时序关键路径是图中黄色反馈路径,需要满足DFF的建立时间T**setup,响应时间T**ck-q,加法器响应时间T**sum三者之和小于1UI时间。

T*setup+Tck-q+Tsum<1UI*

图5是最基本的DFE结构。其中Clk时钟频率和数据率相等(NRZ编码)。称之为全速率(Full-Rate)直接反馈(Direct Feedback)架构DFE。

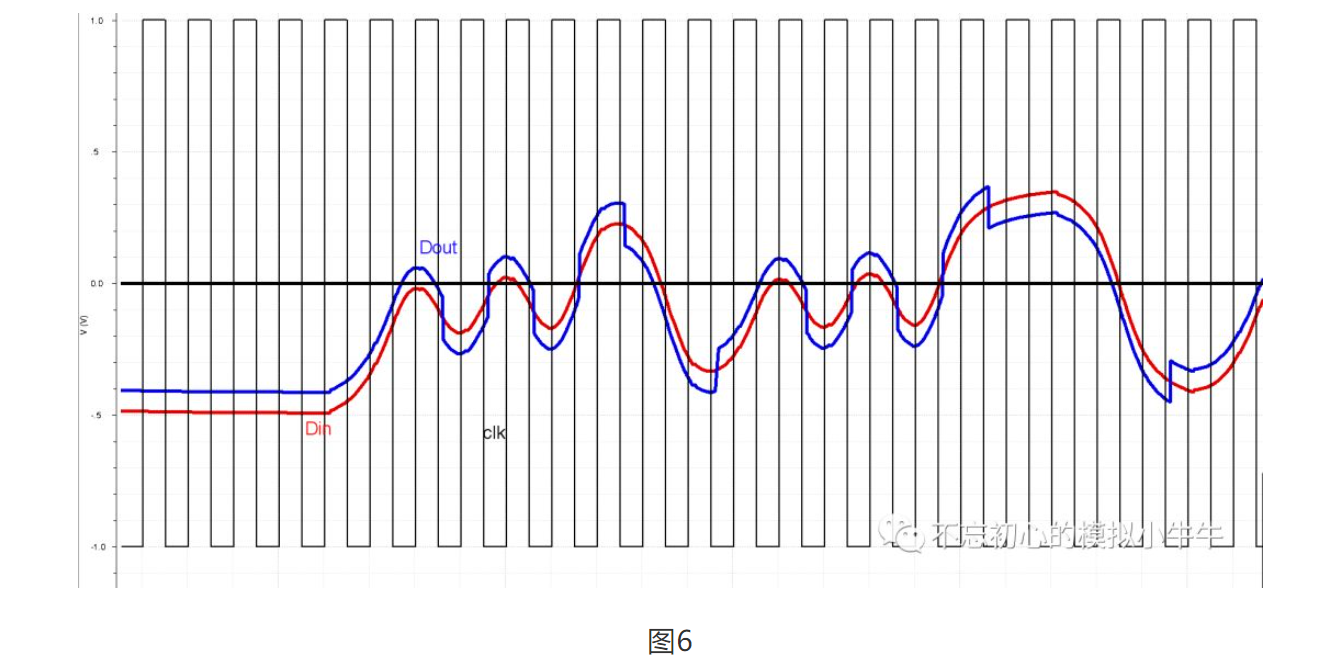

图6给出了全速DFE对信号的均衡效果,Din经过1个Tap补偿后,输出波形Dout。可以看到对于高频数据,其判决幅度明显增大,更大概率判断处正确数据。

Part2 DFE架构介绍

采样DFF的延迟时间T**ck-q并没有明显减小,DFE反馈关键路径时序变得越来越难以满足。因此需要从结构上改进和优化这些问题。

随着数据速率的提高,图5的DFE有很多改进和优化结构。主要从这两方面分类。

首先是采样工作速率,分为全速率(Full-Rate),半速率(Half-Rate),1/4速率(Quarter-Rate)等等。

其次从时序关键路径,分为直接反馈(Direct Feedback)和开环(Loop Unrolled)结构。开环结构也称之为预判(Speculation)结构。预判式(Speculative)结构的Slicer个数会增加一倍。常见的是将h1这条关键路径进行开环,保证时序。在一些文献中,也见到过将前2个Tap全部使用预判结构,缺点是会使用比较多数量的Slicer。

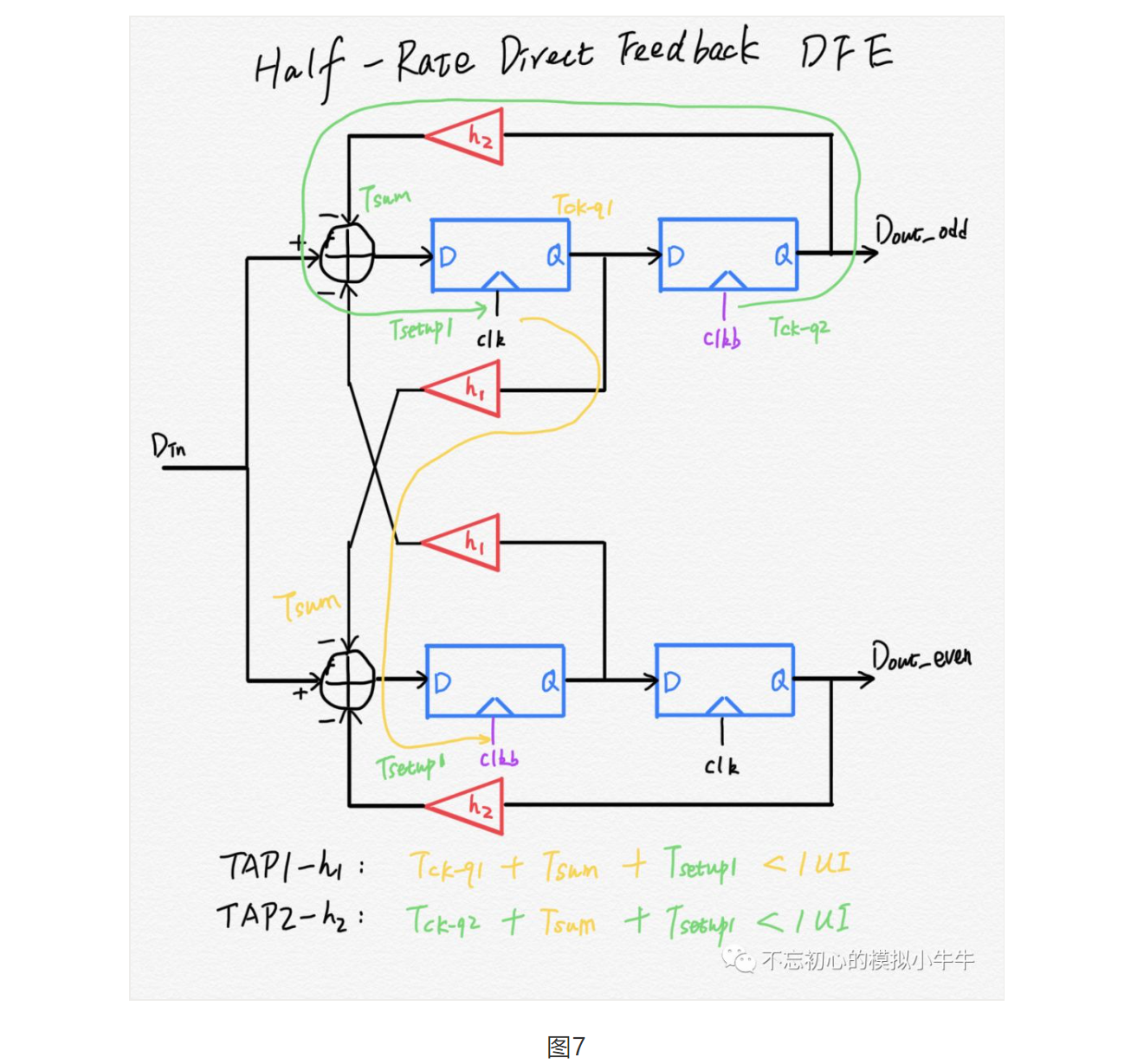

图7是相对于图5结构对应的半速率实现形式,图中包含了h1和h2的时序路径中包含的各时间参数,以及需要满足的时序约束。注意半速率结构的采样时钟是数据率的一半,也就是使用的奈奎斯特频率时钟频率,奇(Odd)偶(Even)分别使用反相时钟clk和clkb进行交替采样。

这里就要思考下采用半速率的得与失了。采用半速率,DFE部分的面积和功耗都会增加,那么优势是什么?其实从系统上看,功耗还是会减低的,主要是时钟产生电路PLL和时钟路径的功耗会有明显的减低。同时更低速时钟频率也能适当降低电路设计难度。

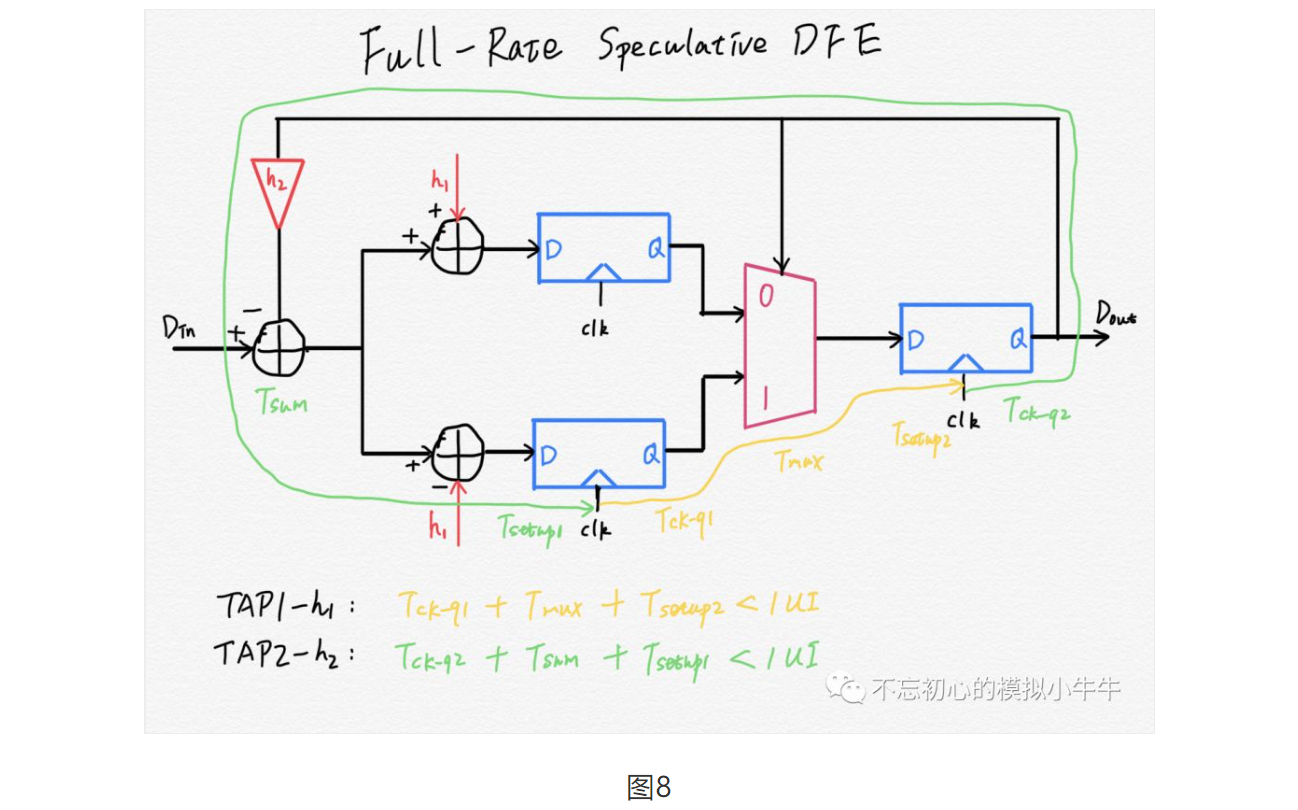

图8为全速率预判式DFE结构图,Tap1采用了预判结构,Tap2直接反馈。可以看到通过提前将h1和输入进行加减,并通过前一码元的结果对当前码元的结果进行选择。可以看到,这里边有3个加法器(Summer),在实际电路实现时,通常将h1的summer和DFF合并,即为包含阈值的Slicer。

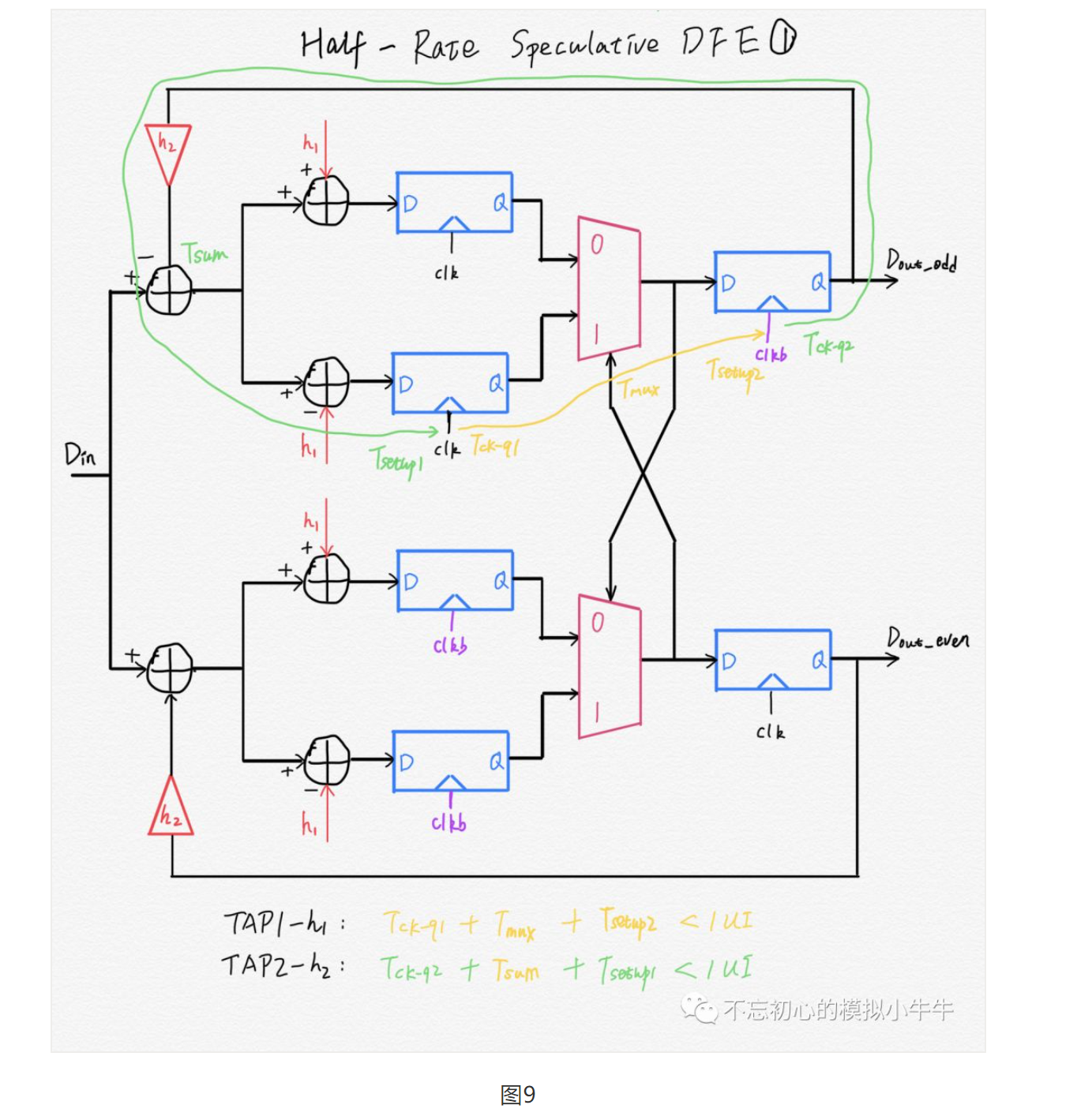

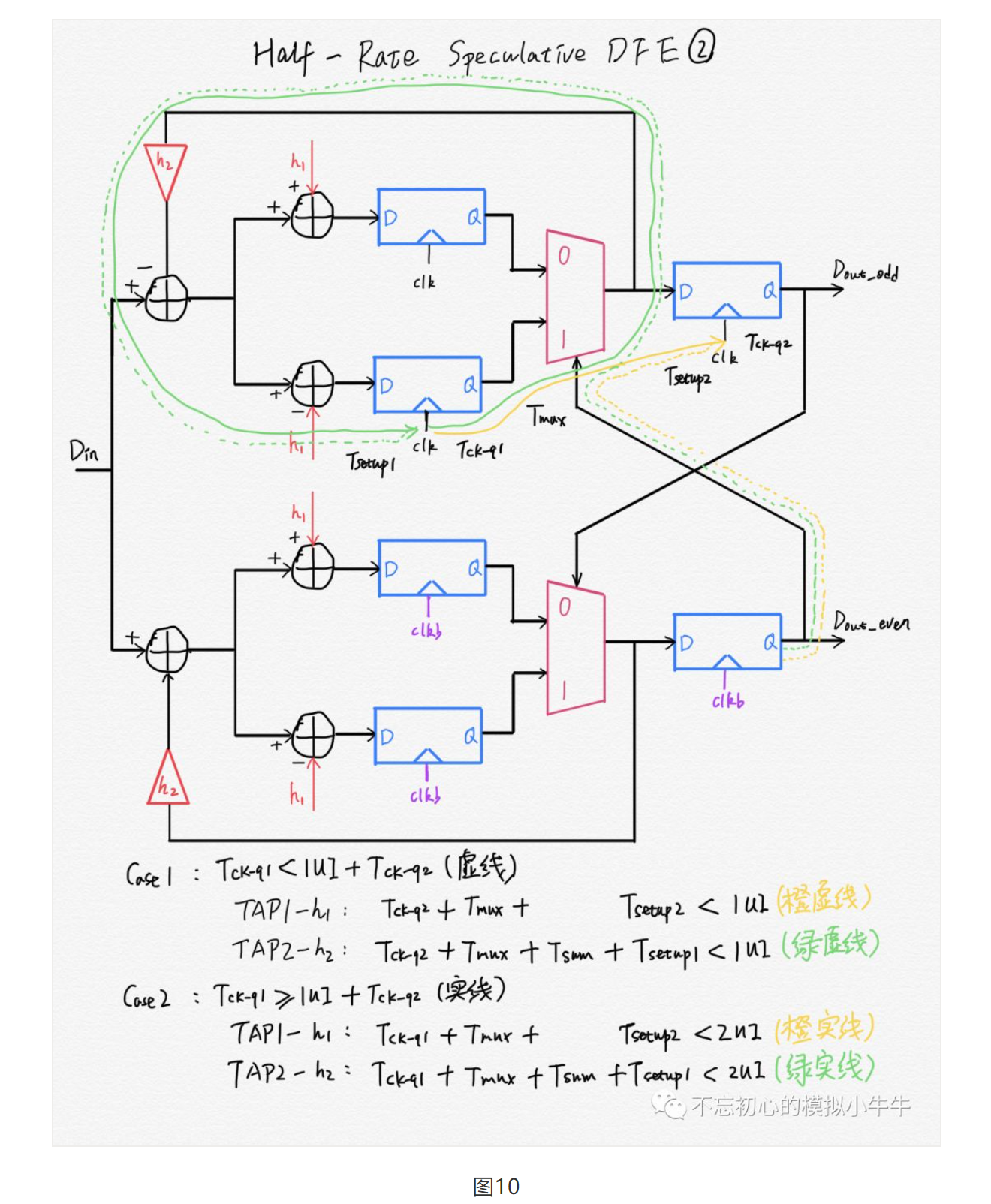

图9和图10为半速率预判式DFE结构,通过将h1提前进行加减,可以节约Tap1路径的时间,增大时序裕量。

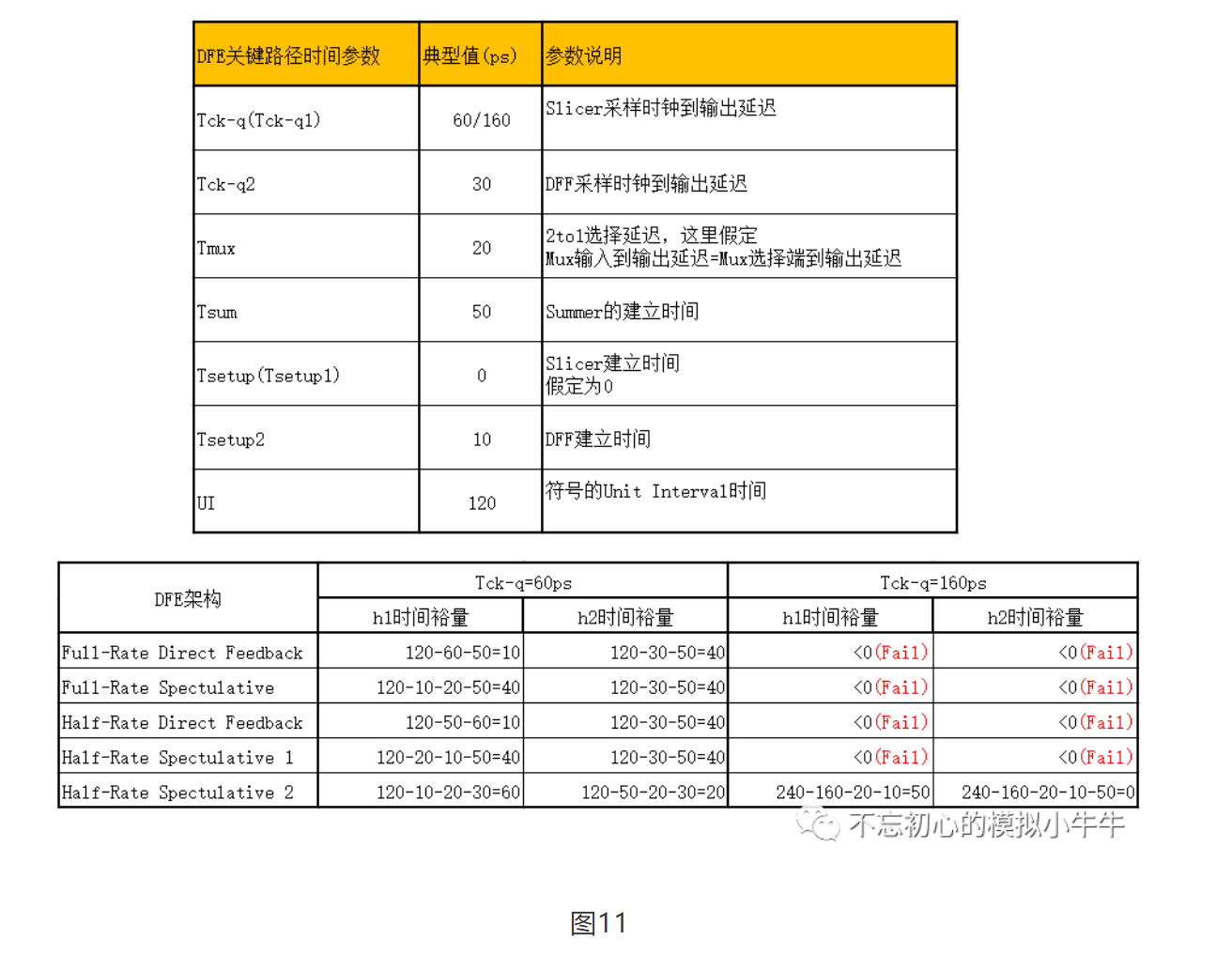

图11给了个典型的例子说明了不同结构的tap1和tap2的时间裕量。以及改进的半速率结构的优势。可以将缩减h2的时间,将h1的时间适当延长,拓展到2UI的时间。

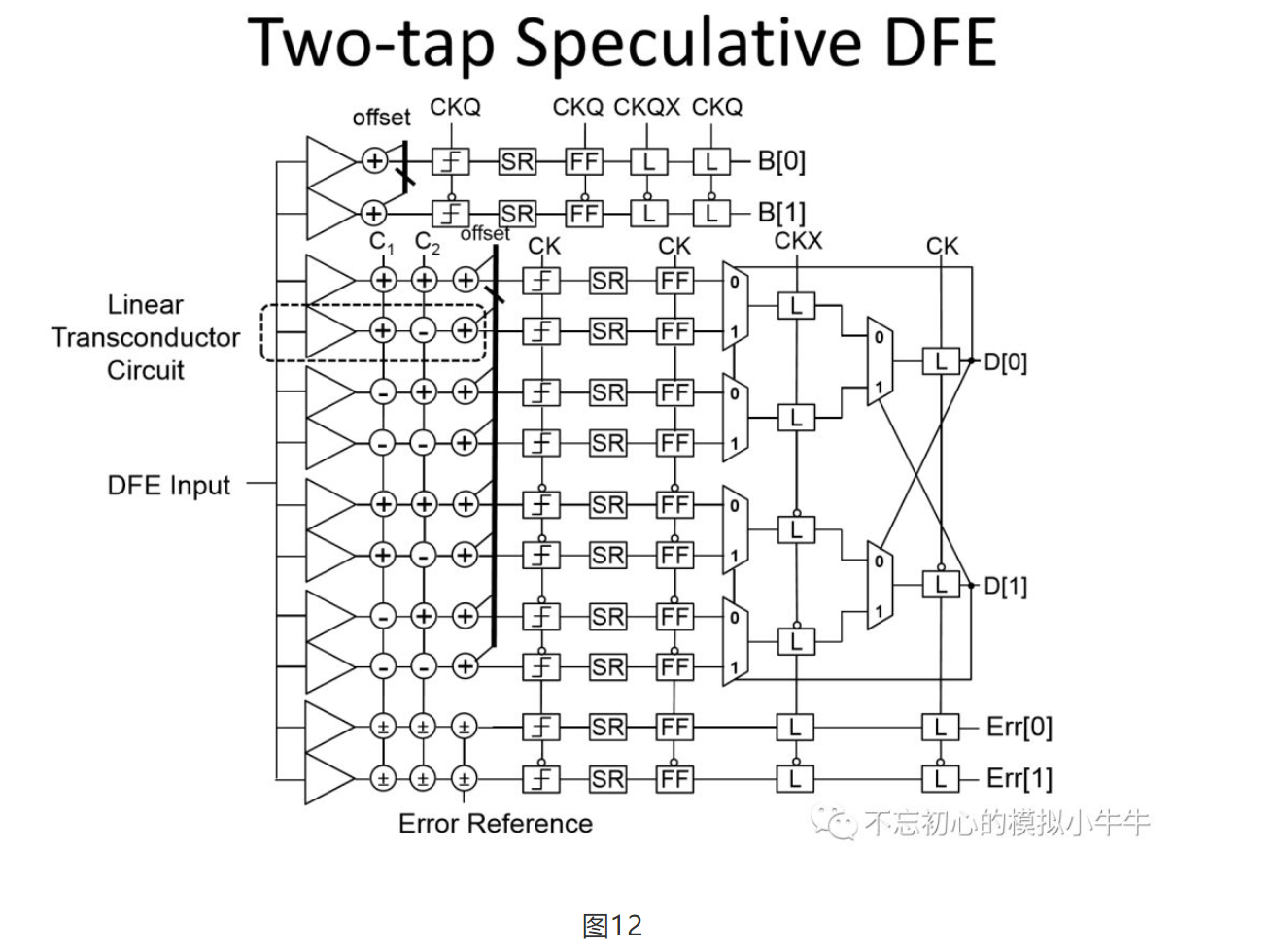

此外,还可以将Tap1和Tap2都提前与信号做加减,也就是2tap-Speculative结构的DFE,如图12。当该结构采用半速率,Data采样共需要8个Slicer。Tap1和Tap2系数C1和C2会提前按照符号和输入信号叠加,采样后利用前边2个码元进行Mux4to1的选择。

实际实现的时候还有一些结构,会把其中的时间进行压缩,进一步提高速度,比如讲Summer和Slicer合并等,降低Summer的延时Tsum。

对于半速率预判式DFE,如果只有一个Tap,可以对奇偶数据进行多拍延迟,然后再做Mux选择。

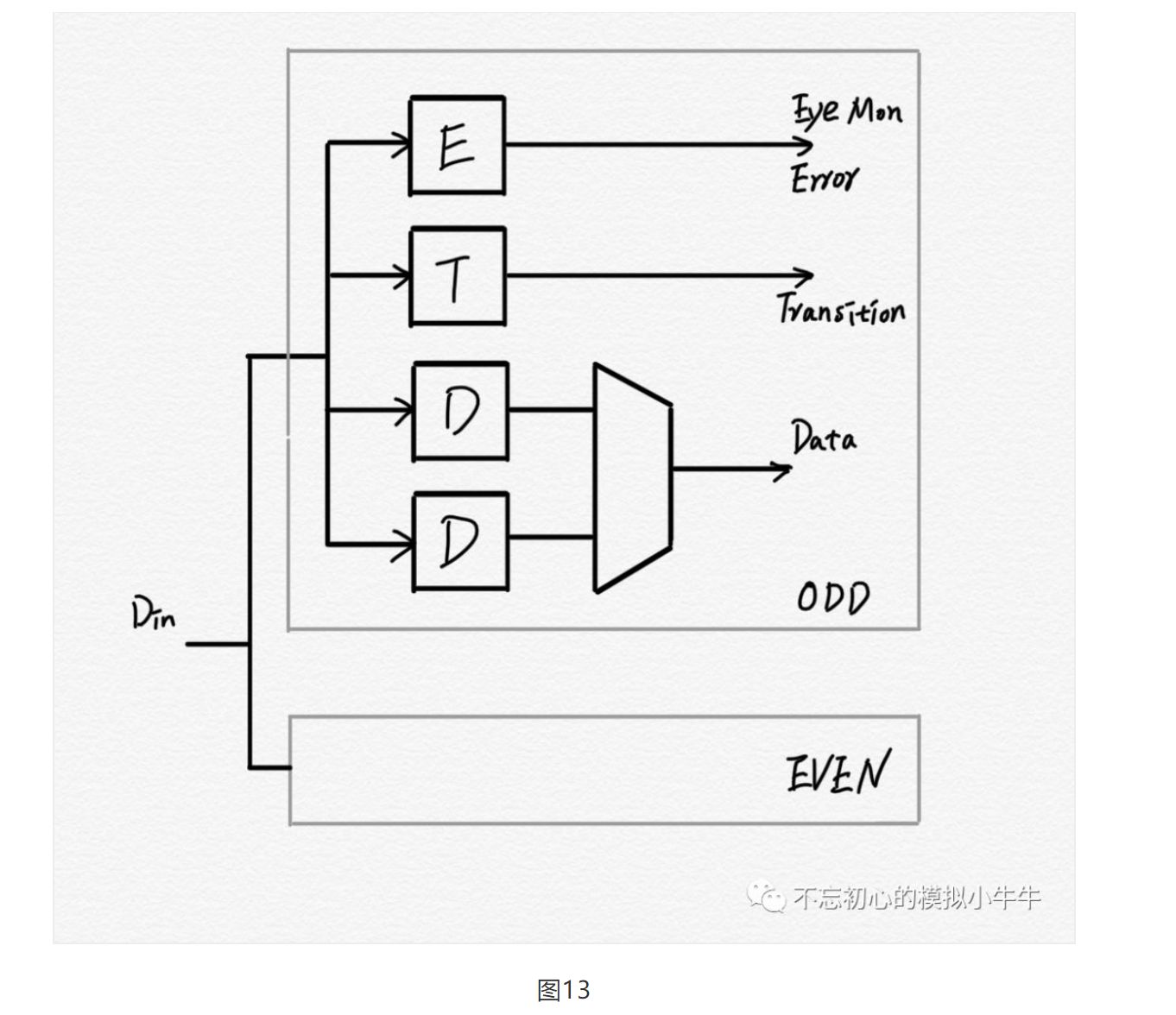

在SerDes中,DFE通常还包含了其他采样器,用于实现DFE的自适应均衡,CDR锁定,LEQ的自适应,通路增益调节,数字眼图测量,Figure of Metric评估等功能,如图13所示。

Part3 关键功能模块

在前两部分内容中,提到DFE结构中最常用的子模块包括采样器Slicer,加法器Summer,选择器Mux,延迟单元DFF&Latch等等,下边我们简单做下介绍。

- Slicer

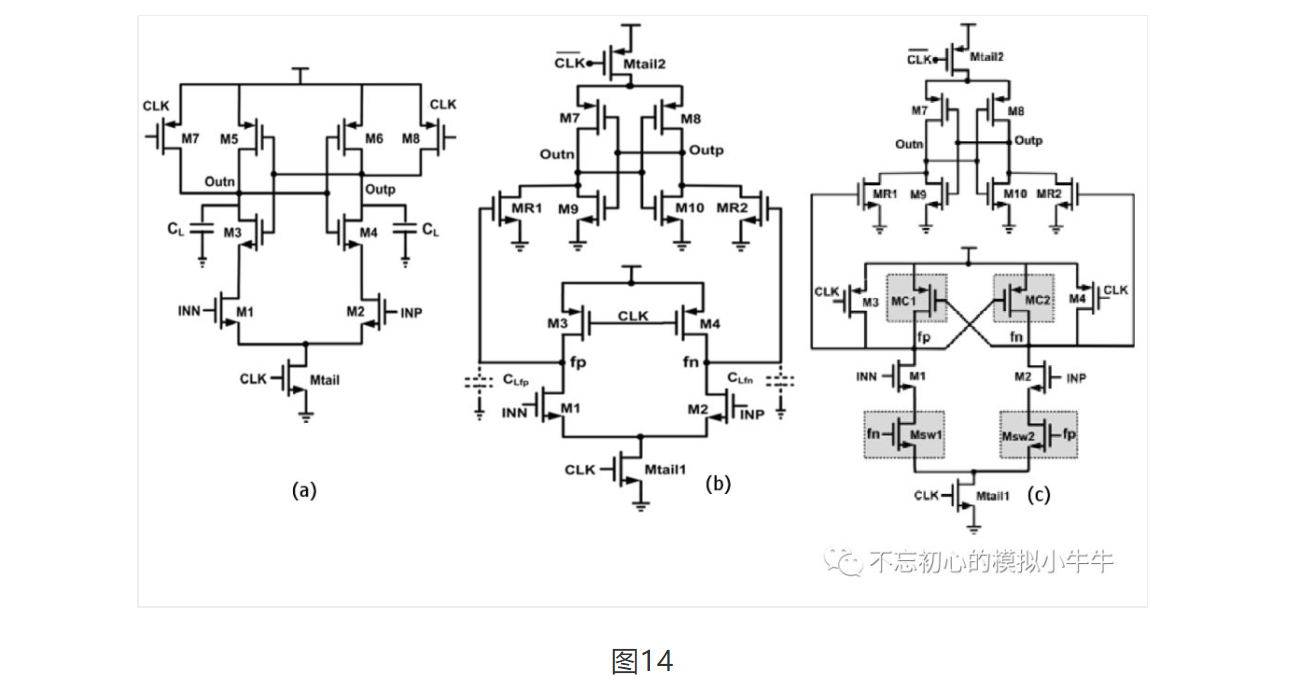

采样器Slicer主要是用于对输入信号的量化,相当于1bit的ADC。量化后的逻辑可以看做恢复后的数据。其结构就是常规的灵敏放大器(Sense Amplifer,SA),或者称之为动态比较器(Dynamic Comparator)。

图14是一些常见的Slicer实现形式。其中(a)是基本类型,(b)是双尾电流(Double-Tail)动态比较器,(c)是改进型的双尾电流动态比较器。设计的重点是提升响应速度,提高输入灵敏度,降低功耗,减小回踢噪声,减小输入失调等。

随着数据率的提高,如何降低动态比较器的输出响应时间,可能是优先级最高的考虑因素,只有保证数据正确,一切才有意义。输出响应时间和工艺制程,输入差分信号幅度,共模电平,电源电压都密切相关。其中先进工艺制程提供的更小的器件尺寸,为高速接口设计提供了最直接帮助。

需要注意到,图14中结构电路,在一个CLK周期的高低电平内,动态比较器需要完成预充电(Precharge)和放大(Amplification)的功能。因为时钟周期的一半是复位状态,因此需要剩余的半个时钟周期内完成采样量化,这里就解释了为什么半速率会比全速率结构能够留给动态比较器有更多的输出响应时间。也就更大概率分辨较小的输入信号,并得到正确数据。

动态比较器的输出只能保持少半个采样周期的输出数据,通常我们还需要另外的保持电路,”接棒”动态比较器输出,从而将采样结果保持一整个采样周期。

这也就是我们在图5到中提到的,用DFF的概念表示对数据采样和保持的功能。实际上我们用经常使用的概念Slicer,也可以泛指动态比较器和”接棒”的延迟单元。

- DFF & Latch

前边提到的Slicer中需要的延迟单元,可以是Latch,也可以是DFF。当然DFF可以看做是两个Latch结构的级联。

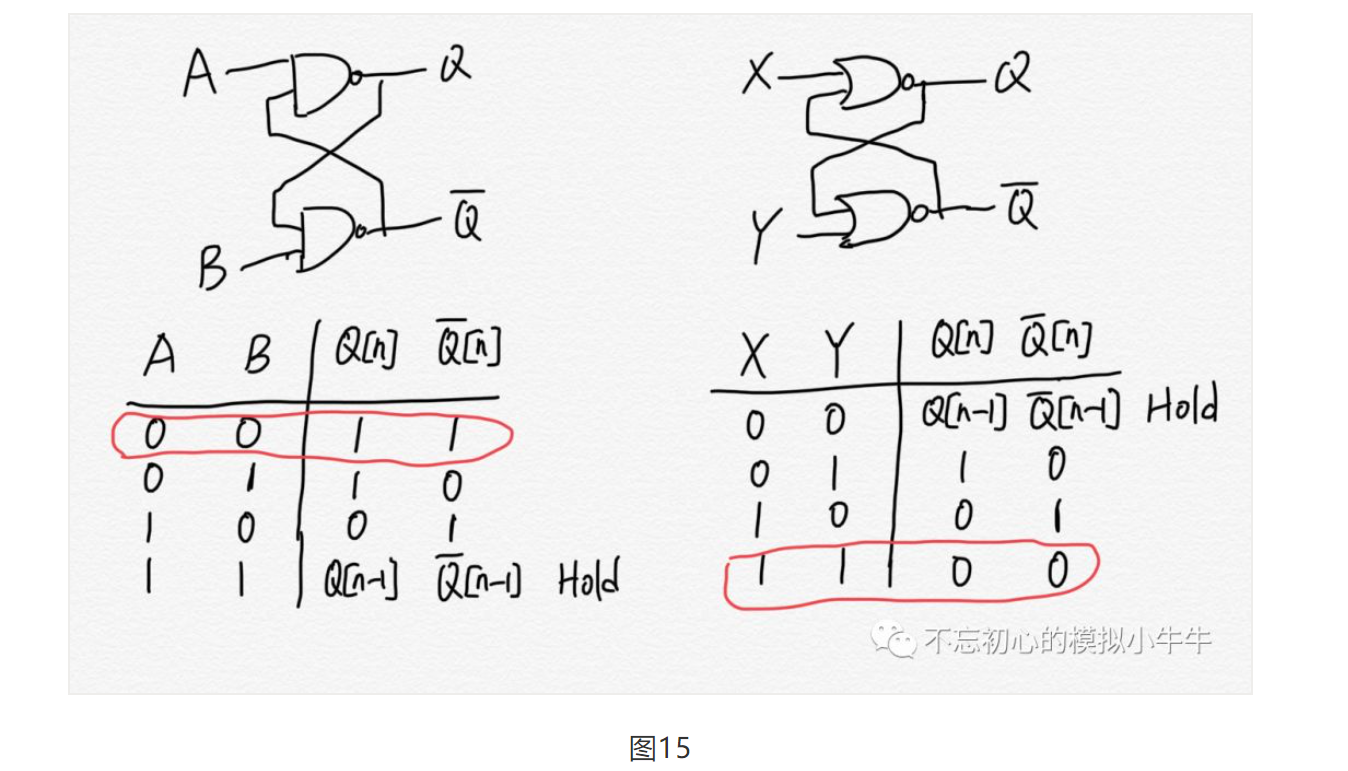

提到Latch,我们最先想到SR锁存器。可以由NAND2组成,也可以是NOR2组成的。基本的SR Latch不需要时钟,仅根据输入信号的变化,有不同的输出状态。如图15所示,两种结构的保持(Hold)状态的输入时不同的,可结合动态比较器的结构选择使用。

图15

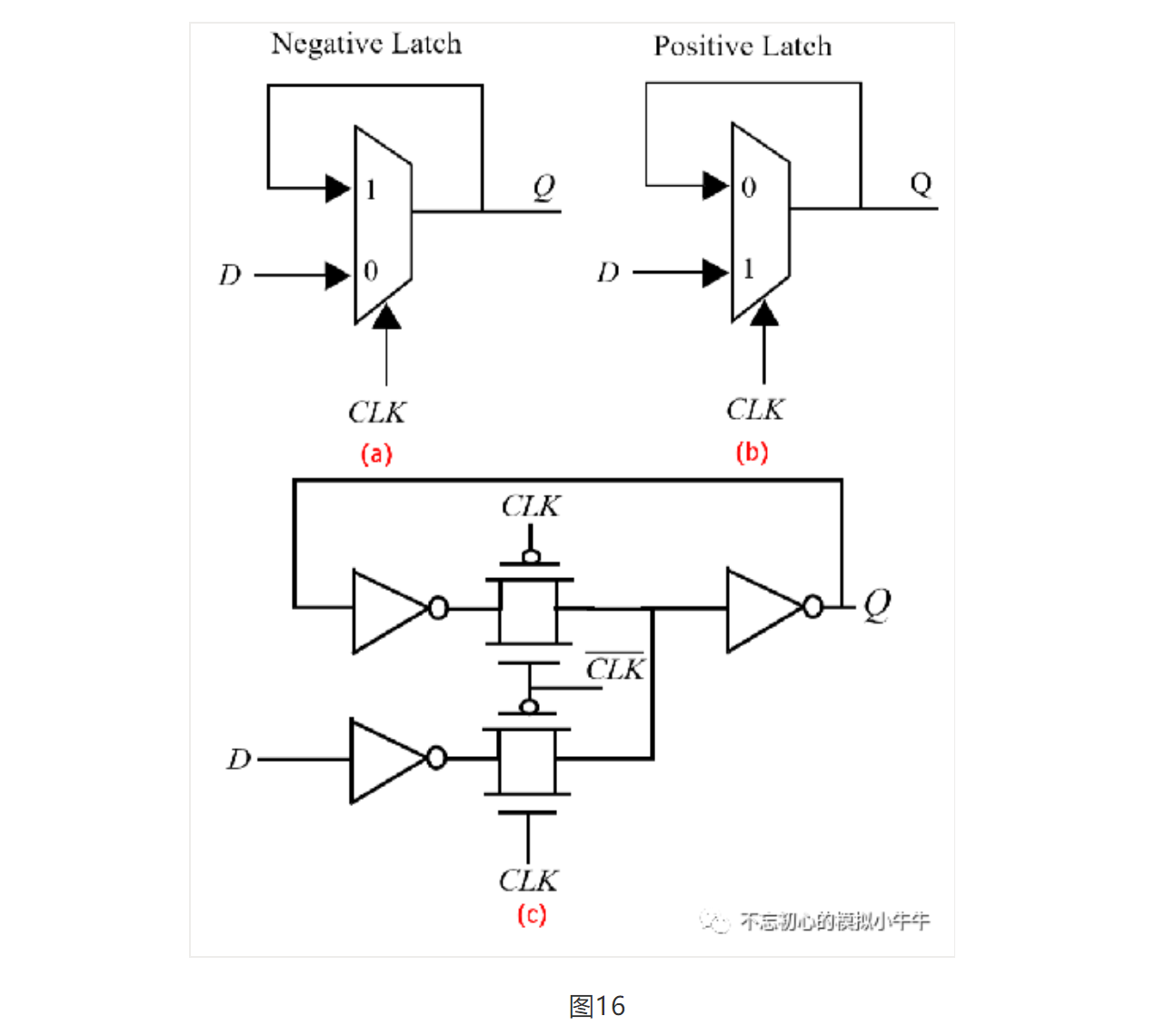

基于选择器的锁存器(Multiplexer-Based Latch)由传输门选择器和反相器构成的,通过时钟进行控制。如图16所示,(a)和(b)分别是高电平锁存器和低电平锁存器。图中(c)是选择器和反相器的实现细节。

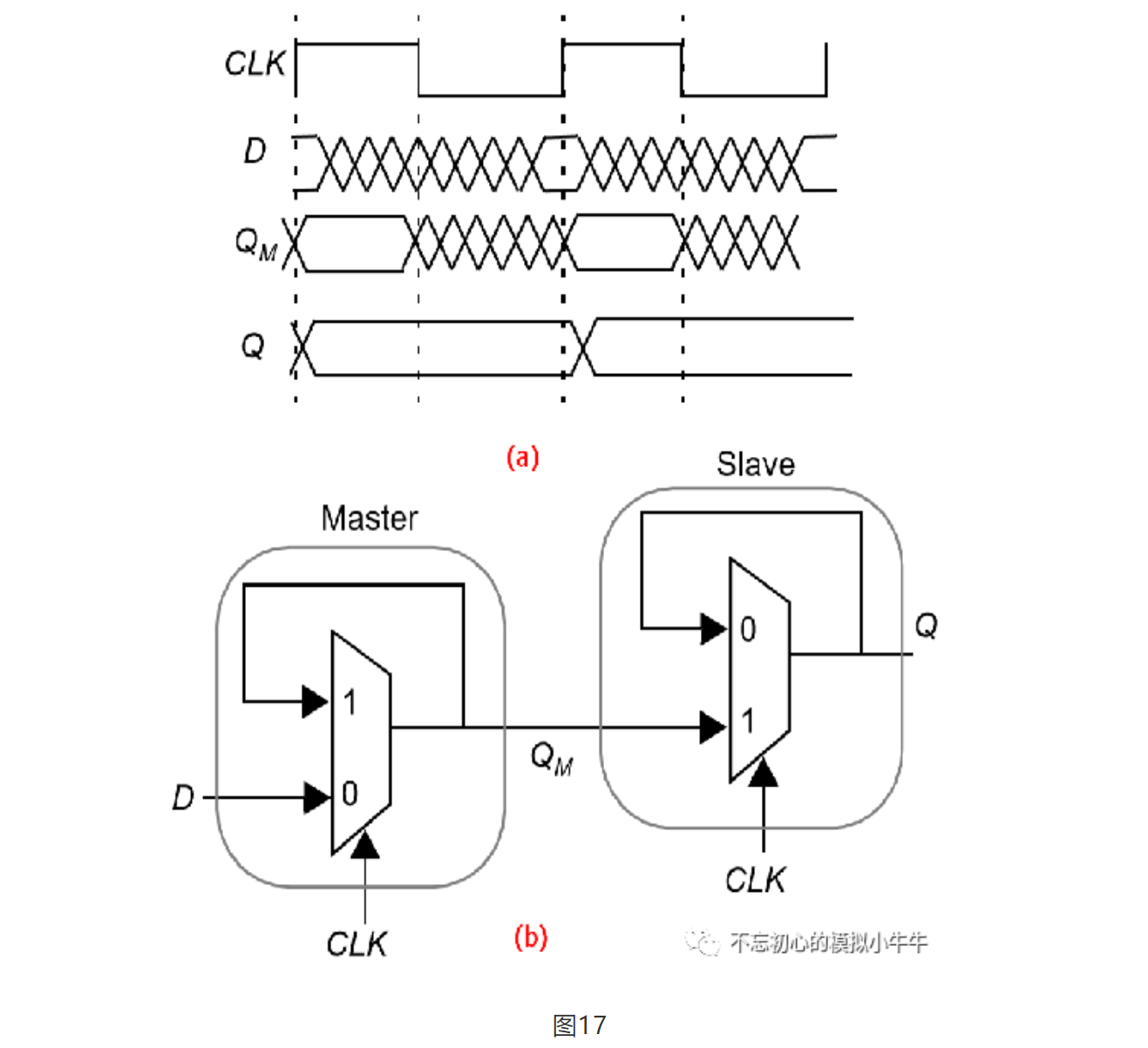

将图16中的高低电平锁存器进行先后级联,可得到主从边沿触发触发器(Master-Slave Edge-Triggered Flip-Flop)。触发方式可以是上升沿,也可以是下降沿。其时序和结构如图17中(a)和(b)所示。

除了上述的CMOS电平锁存器外,文献中常见的还有半电平的CML锁存器。

- Summer

加法器目的是完成输入Din和Tap量hn的加减操作。

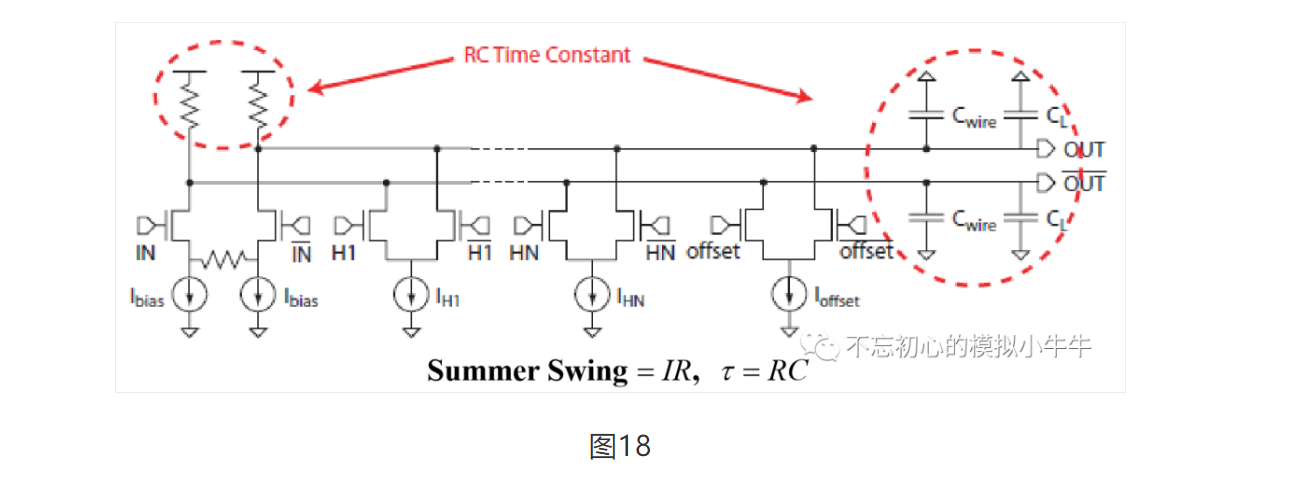

图18所示CML结构电阻负载(Resistor Load)加法器,各Tap量通过电流相加,并通过电阻转化为电压信号供Slicer采样比较。电阻负载的结构存在输出摆幅,功耗,建立时间的考虑,其建立时间由输出节点的时间常数tau决定。例如3tau可以建立约95%的精度。主要影响了时序参数Tsum

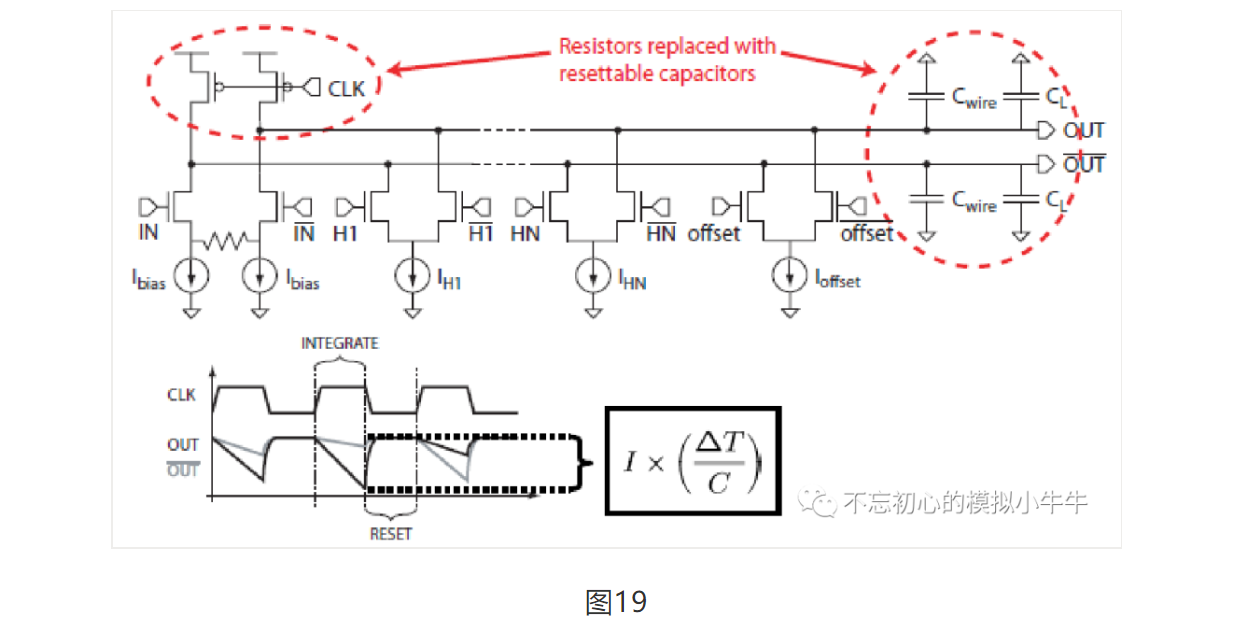

图19是电流积分(Current Integrating)型加法器,通过时钟对负载电容CL进行复位和积分的分阶段重复操作。输出为归零(Return to Zero,RZ)信号。该结构比电阻负载加法器有着更高的能效,但文献中提到,该结构会存在3.9dB的直接积分损耗。

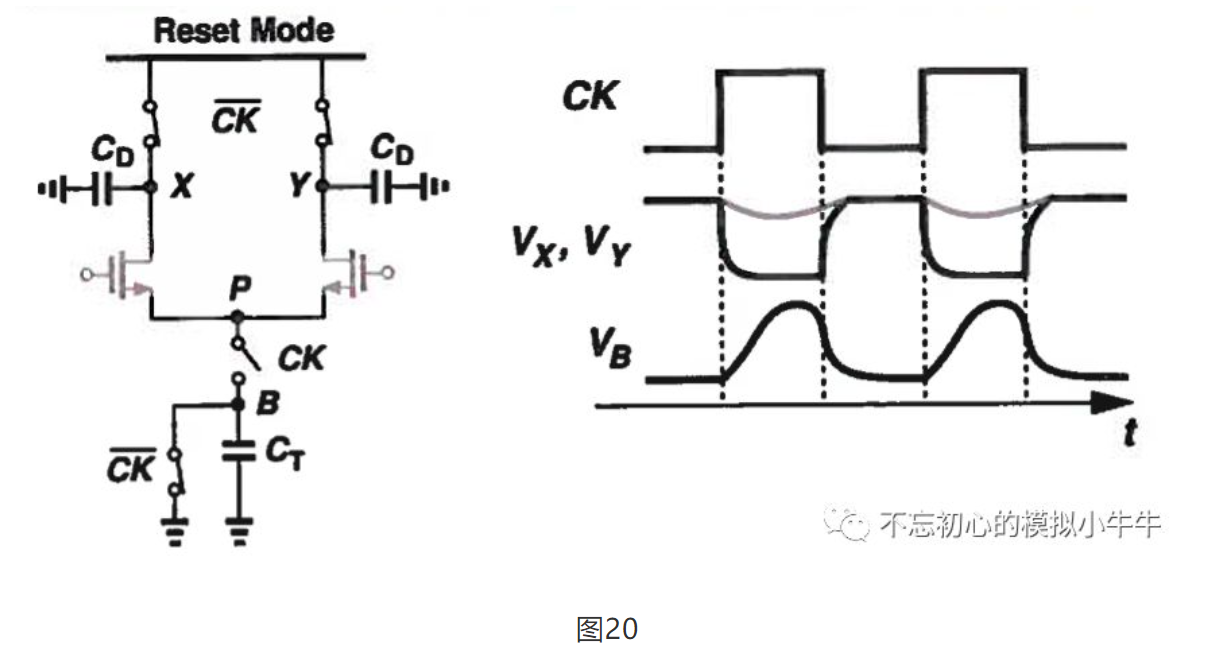

图20是电荷舵(Charge Steering)型加法器。Razavi提到过该结构具有零静态功耗,同时动态功耗显著下降的新型加法器实现。复位阶段X和Y点被复位到电源,因此查分输出Vx-Vy实际上也可以看做RZ信号。

需要注意,DFE补偿为了实现一定的精度,Tap量hn通常使用IDAC来实现,速度会比较快。不同tap的精度和范围会有差异。

- Mux

Mux本身的功能比较简单,目的就是将多路数(更多的是将2个路径数据)选择输出。可以直接用传输门结构,或者用具有3态控制的反相器实现即可,这里就不举例说明了。

- Merged Structure

除了以上基本的结构,在一些文献中还提到了混合型结构,从而可以进一步缩减tap反馈路径的时间。

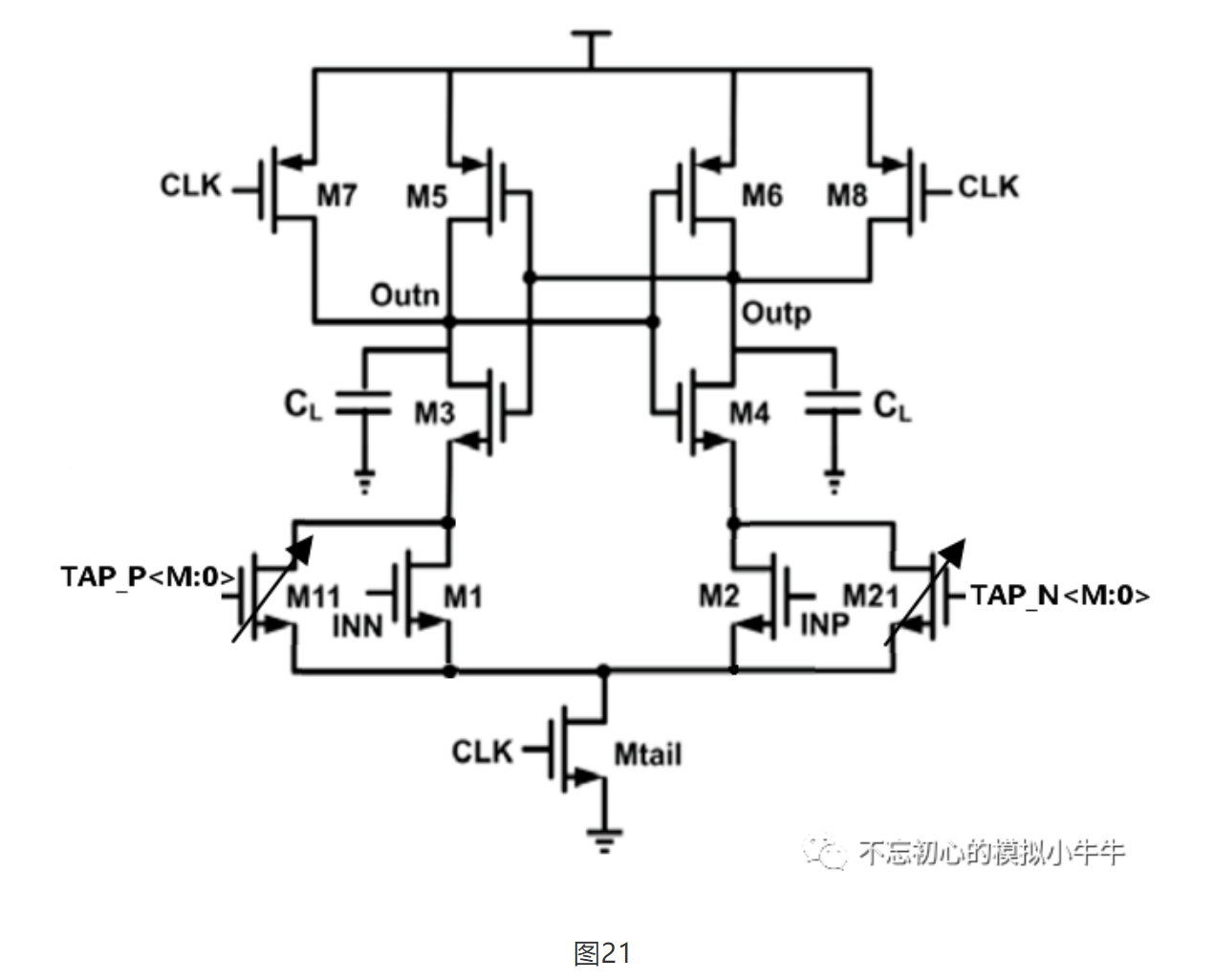

图8中提到的带阈值的Slicer,就算作是混合结构。tap1权重h1的加法Summer和Sampler融合。结构如图21。通过DAC属猪的tap电压或者直接用逻辑控制输入对管M11和M21,实现对输入信号的Tap补偿。其中用逻辑直接控制的结构尤其适合低功耗场景下的1个Tap的预判式DFE设计,毕竟是牺牲了一定的速度和精度,才实现了低功耗的目的。

前文提到的Slicer概念,其实也可以看做是Sampler和延迟单元Latch的合并的混合结构。